www.acsami.org

# Single CuO<sub>x</sub> Nanowire Memristor: Forming-Free Resistive Switching Behavior

Kai-De Liang,<sup>†,§</sup> Chi-Hsin Huang,<sup>†,§</sup> Chih-Chung Lai,<sup>†</sup> Jian-Shiou Huang,<sup>†</sup> Hung-Wei Tsai,<sup>†</sup> Yi-Chung Wang,<sup>†</sup> Yu-Chuan Shih,<sup>†</sup> Mu-Tung Chang,<sup>‡</sup> Shen-Chuan Lo,<sup>‡</sup> and Yu-Lun Chueh\*,<sup>†</sup>

Supporting Information

**ABSTRACT:**  $\text{CuO}_x$  nanowires were synthesized by a low-cost and large-scale electrochemical process with AAO membranes at room temperature and its resistive switching has been demonstrated. The switching characteristic exhibits forming-free and low electric-field switching operation due to coexistence of significant amount of defects and Cu nanocrystals in the partially oxidized nanowires. The detailed resistive switching characteristics of  $\text{CuO}_x$  nanowire systems have been investigated and possible switching mechanisms are systematically proposed based on the microstructural and chemical analysis via transmission electron microscopy.

KEYWORDS: CuO<sub>x</sub> nanowire, ReRAM, AAO membrane, resistive switching, forming free, memristor

## 1. INTRODUCTION

Resistive switching random access memory (ReRAM) based on electrical resistance switches, so-called memristors, is one of the most promising candidates for next generation nonvolatile memory due to its high stacking density, low power consumption, high scalability, fast fabrication process, and multistate behaviors.<sup>1–4</sup> The resistive switching phenomena in transition metal oxides, such as NiO,<sup>5</sup> TiO<sub>2</sub>,<sup>6</sup> ZnO,<sup>7,8</sup> and Cu<sub>2</sub>O<sup>9</sup> based on two-dimensional (2D) metal-insulator-metal (MIM) thin film structures, have been demonstrated. However, the conventional lithography has encountered the physical limit when the size of the devices is scaled down to the nanoscale. To reduce the size of the devices to achieve a higher density and improve the device performance, finding the unique properties of nanostructures is a useful way to explore the unclear nanoscale resistive switching mechanisms to understand the scalability of ReRAM. 10-14

One-dimensional (1D) nanostructures, especially semiconductor nanowires (NWs), have drawn much attention for various nanoelectronic applications due to their unique physical and chemical behaviors, which are different from their bulk and thin film materials, in confined dimensions and large surface-to-volume ratios. In recent years, top-down or bottom-up approaches have been applied to synthesize various nanostructures, including nanotubes, nanowires, and nanodots for the fabrication of nanoscale devices. The resistive switching characteristics of nanostructure materials, such as NiO NW, 18-20 Co<sub>3</sub>O<sub>4</sub> NW, 21 ZnO NW, 22,23 Cu<sub>2</sub>O NW, 21 Zn<sub>2</sub>SnO<sub>4</sub> NW, 25 and gold—Ga<sub>2</sub>O<sub>3</sub> NW, 26 have attracted great interest in ReRAM studies.

For a large area and low-cost process, the self-assembly bottom-up approach via different templates is more promising for synthesis of nanostructures than the top-down approach.<sup>27</sup> An anodic aluminum oxide membrane (AAO) is one of selforganized templates used to form various nanostructures due to its controllable pore-diameter, depth, shape, and periodic pattern, respectively.<sup>28,29</sup> Fabricated nanowire arrays by electrochemical synthesis combined with an AAO membrane is a room-temperature and low-cost, large-scale process for the production of nanoscale electronic devices. In addition, Cu is a common material for interconnects in the integrated circuit (IC). A CuO<sub>x</sub> nanowire is anticipated to have high compatibility with modern complementary metal-oxidesemiconductor (CMOS) manufacturing techniques. In this regard, we demonstrate direct synthesis of CuO<sub>x</sub> nanowire arrays from Cu NW arrays embedded in the AAO and each single CuO<sub>x</sub> nanowire as a memristor exhibits a forming-free behavior. The CuO<sub>r</sub> NWs were formed by the thermal annealing of Cu nanowire arrays that were deposited in the AAO membrane by an electrochemical plating approach. The detailed resistive switching characteristics of CuO, NW systems have been investigated. Finally, we systematically propose possible switching mechanisms on the basis of the microstructural and chemical analysis via transmission electron microscopy (TEM).

Received: May 7, 2014 Accepted: August 27, 2014 Published: August 27, 2014

<sup>&</sup>lt;sup>†</sup>Department of Materials Science & Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan

<sup>\*</sup>Material and Chemical Research Laboratories, Industrial Technology Research Institute, Hsin-Chu 31040, Taiwan

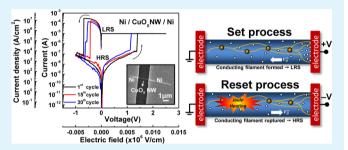

Figure 1. Schematics of the fabrication processes of  $CuO_x$  NW array. (a) Free-standing AAO with high aspect ratio nanochannels, (b) Ni conductive layer deposited by e-beam evaporation, (c) Cu NW array synthesized by pulse electrodeposition, and (d) oxidation process.

#### 2. EXPERIMENTAL SECTION

**2.1. Synthesis of AAO.** To fabricate an anodic aluminum oxide (AAO) template with a pore diameter of ~50 nm, a two-step anodization process was usually used. Before the anodization, highpurity Al (99.997%) sheets were sliced into 1 × 2 cm samples. Then, these samples were electropolished in a perchloric acid (HClO<sub>4</sub>)/ $C_2H_5OH$  (1:4 in volume) solution for a few seconds at 10 °C. In the first step, the pretreated Al samples were anodized at a constant voltage of 40 V in 0.3 M oxalic acid ( $H_2C_2O_4$ ) solution for 30 min at 10 °C. The previously formed AAO films were etched in a mixed solution of 0.2 M  $H_2CrO_4$  and 0.4 M  $H_3PO_4$  for 30 min at 60 °C. After that, the second anodization was performed for 10 h. Besides, a current limited anodization method was utilized for thinning the barrier layer at the bottom of anodic porous alumina templates.

2.2. Electrochemical Deposition of Cu Nanowire Array from **AAO Template.** Anodic aluminum oxide (AAO) ~50 nm in diameter was used as the template for the electrochemical deposition of Cu NW arrays. To make sure the electric contact, a thin nickel (Ni) layer (about 200 nm) serving as working electrode was deposited on the one side of the AAO template by electron beam evaporation in a vacuum of  $\sim 5 \times 10^{-6}$  Torr. The electrodeposition of copper nanowires was carried out in an electrolyte, containing 0.7 M CuSO<sub>4</sub>·5H<sub>2</sub>O (99.5%, SHOWA) and deionized (DI) water with a pH value between 3 and 4. Electrochemical depositions were performed at room temperature (RT) using a galvanostatic pulse technique in a two-electrode electrochemical cell, having a graphite counter electrode. Magnetic stirring was applied to improve the diffusion of Cu ions at the cathode. The rotation speed was limited to avoid formation of air bubbles into the electrolyte. The Cu NWs electrodeposition process was based on modulated pulse signals in the microsecond range. During the pulse of negative current (-0.4 A, 10 ms), Cu nanowires were deposited. After the pulse deposition, a zero-bias of 50 ms was used to recover the ion concentration. The deposition process mentioned above was called a cycle. The resulting length of NWs was about 20 um.

**2.3.** Formation of  $CuO_x$  Nanowire Arrays by Oxidation Process.  $CuO_x$  nanowire arrays were synthesized by electrodepositing Cu NWs in the pores of AAO templates. The sample was oxidized at 400 °C for 10 h/20 h in the oxygen ambient to obtain partially oxidized  $CuO_x$  nanowires/fully oxidized  $CuO_x$  nanowires. Next, the AAO membrane was dissolved in a 1 M NaOH solution for 2 h at room temperature. The release of NWs was accelerated by sonication during the 5 s dissolution process. The NWs were then transferred and stored in pure ethanol to get a  $CuO_x$  nanowire solution.

**2.4. Device Fabrication Process.** For the electrical resistive switching properties measurements, typical  $\text{CuO}_x$  and Cu nanowires were drop-casted on a 200 nm thick  $\text{SiO}_2/\text{Si}$  substrate. The Ni electrodes with a thickness of 100 nm were deposited by e-beam evaporation and patterned by photolithography and lift-off processes. A typical distance between two electrodes was ~2  $\mu$ m. Before evaporation of Ni (with a purity of 99.995% and in a vacuum at a pressure lower than  $10^{-6}$  Torr), the sample was dipped into diluted hydrofluoric acid for 10 s to completely remove native oxide in the contact region.

**2.5. Characterization.** Field emission scanning electron microscopy (FE-SEM, JSM-6500F, JEOL), operating at 15 kV and field emission transmission electron microscopy (FE-TEM, JEM-3000F, JEOL) equipped with an energy dispersion spectrometer (EDS), operating at 300 kV were used to study surface morphologies and microstructures. X-ray diffraction spectrometry (Shimadzu XRD 6000, Cu K $\alpha$  radiation with a wavelength of 0.154 nm) was performed to characterize crystal structure. The resistive switching characteristics of the fabricated devices were measured by using a Keithley 4200 semiconductor parameter analyzer in atmospheric air at room temperature.

## 3. RESULTS AND DISCUSSION

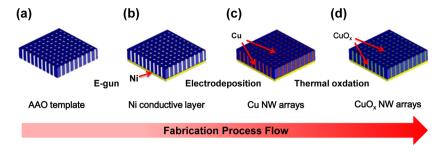

The schematics for the fabrication procedures of CuO<sub>x</sub> nanowire arrays are shown in Figure 1. Detailed fabrication procedures have been mentioned in the Experimental Section. Figure 2a shows a field emission scanning electron microscopy (FE-SEM) image of the fabricated AAO membrane. Note that the ~50 nm pore size can be confirmed. After the Cu NW growth and the oxidation process, CuO<sub>r</sub> nanowire arrays can be achieved in pores of AAO membranes, as shown in Figure 2b. The corresponding X-ray diffraction (XRD) patterns were used to examine the phase of Cu NW arrays before and after annealing, as shown in Figure 2c. Peaks at  $2\theta = 43.3^{\circ}$ ,  $50.4^{\circ}$ , and 74.08°, corresponding to (111), (200), and (220), were found, confirming the NW being of the Cu phase before annealing. After annealing as-grown Cu NW arrays at 400 °C for 10 h, The diffraction peaks at  $2\theta = 35.56^{\circ}$ ,  $38.76^{\circ}$ , and 66.22° indicate the  $(\overline{1}11)$ , (111), and  $(\overline{3}11)$  plane orientations from the CuO phase whereas the diffraction peaks at  $2\theta$  = 36.46° and 42.36° indicate the (111) and (200) plane orientations from the Cu<sub>2</sub>O phase, respectively. The results indicate that copper oxide nanowires synthesized by oxidizing the Cu nanowires consist of three phases, including, Cu, Cu<sub>2</sub>O, and CuO, respectively.

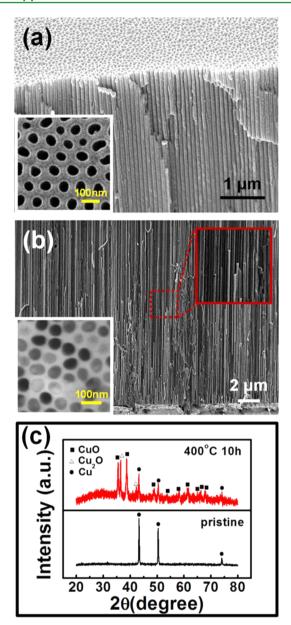

To further shed light on oxidized phases after the oxidation process in order to discover the oxidation mechanism, a TEM image of a single NW is imperative. Figure 3a shows a low magnified TEM image of a Cu nanowire with a diameter of  $\sim$ 50 nm. Obviously, polycrystalline feature was observed for the as-grown Cu NW. The corresponding high-resolution TEM (HRTEM) image shown in Figure 3b, taken from the rectangular region in Figure 3a, clearly indicates formation of many twinned structures. The results also agree with selected area electron diffraction (SAED) pattern obtained by fast Fourier transform (FFT), as shown in inset whose (111), (200), and (220) planes belong to Cu FCC structure. The streaks along symmetric spots found in the SAED again confirm the formation of twinned structures. Figure 3c shows a TEM image of an oxidized CuO<sub>x</sub> NW after the oxidation process. The diameter of the oxidized CuO<sub>x</sub> nanowire still remains

Figure 2. Cross-sectional and top view (inset) SEM images of the assynthesized samples. (a) AAO nanotemplate with a pore diameter of  $\sim$ 50 nm and an interpore distance of  $\sim$ 100 nm. (b) Cu NW arrays embedded in AAO. (c) XRD spectra of Cu NW array in AAO before and after annealing under oxygen ambient.

unchanged due to confinement by the AAO membrane during the oxidation process. From the HRTEM image and corresponding SAED of CuO<sub>x</sub> nanowire shown in Figure 3d, the (111) plane of Cu and Cu<sub>2</sub>O and the (111) plane of CuO were indexed, confirming the presence of polycrystalline CuO<sub>x</sub> phases, containing Cu, Cu<sub>2</sub>O, and CuO phases together, which is consistent with XRD results. To further confirm the mixed phases of the CuO<sub>x</sub> NW, electron energy loss spectrum (EELS) mapping was used. As shown in the inset of Figure 3e, the different contrasts of the O K-edge and Cu L-edge related to CuO<sub>x</sub> nanowire were acquired. As can be seen in the EELS O K-edge image, the signal of oxygen in the outer nanowire was obviously stronger than that in the inner nanowire, revealing that the shell of the nanowire is more oxidized. In addition, nonuniform distribution oxygen in the core of the nanowire

was observed, further indicating that the NW was partially oxidized. The results were also confirmed by high angular dark field (HAADF) imaging, as shown in the inset of Figure S1 (Supporting Information) in which the image contrast is mainly determined by scatting behavior of electrons because of the different atomic mass. The larger the atomic number, the brighter the image. As a result, the darker image contrast in the outer region compared with brighter image contrast in the core region is indicative of partial oxidation of the Cu NW, which is consistent with the chemical analysis. Moreover, a distinctive difference between Cu and  $\text{Cu}^{2+}$  shown in Cu  $\text{L}_{2,3}$  edge EELS spectra also provide an evidence (Figure S1, Supporting Information). Therefore, we postulate that the partially oxidized  $\text{CuO}_x$  nanowire arrays with embedded Cu nanocrystal have been synthesized by the AAO annealing method.

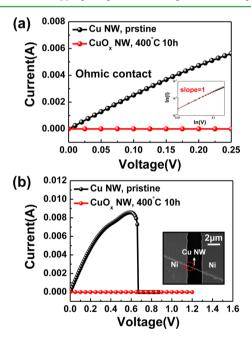

To investigate the intrinsic property of the CuO<sub>x</sub> nanowire, two-terminal electric measurements on the single CuO<sub>x</sub> NW bridged by Ni electrodes in DC voltage sweep mode were carried out by applying a voltage on one electrode while the another electrode was grounded. For comparison, the Ni/Cu NW/Ni devices were fabricated as well. All current-voltage (I-V) curves of Cu NWs and CuO<sub>x</sub> NWs were measured in atmospheric air at room temperature. Figure 4a shows the distinctive I-V characteristics between Cu and CuO<sub>x</sub> NWs under a small positive bias, respectively. The inset shows the corresponding SEM image of the device. The Cu NW, the resistance of which is about  $\sim$ 40  $\Omega$ , exhibits a conducting linear ohmic behavior whereas the CuO<sub>x</sub> NW shows a nonconducting characteristic. The pristine device exhibits a resistance of about 65 M $\Omega$ , which is much higher than the resistance of Cu NW. As the applied bias exceeds the critical value, a dramatic drop in current is observed in Figure 4b for the Cu NW. Before that, a maximum current of ~8.57 mA can be measured at an applied bias of ~0.66 V under a sweeping rate of 10 mV per step. In our opinion, Cu NW would break down due to the thermal Joule heating effect. The corresponding SEM image is shown in the inset of Figure 4b after the nanowire breakdown. In addition, the Joule heating produced by the large current will increase the temperature of the nanowire to amplify the electron-phonon scattering when electrons transport in Cu NW<sup>31-33</sup> and make Cu NW oxidized slightly, leading to a decrease of electron transport behavior in Cu NWs. The electron-phonon scattering effect and Cu oxidation explain a nonlinear behavior from I-V curves when we applied the increasing positive bias, as shown in Figure 4b. In contract, the resistance of the CuO<sub>x</sub> NW is relatively high and stable in the similar voltage range.

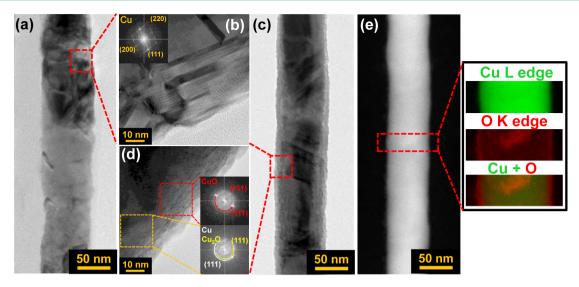

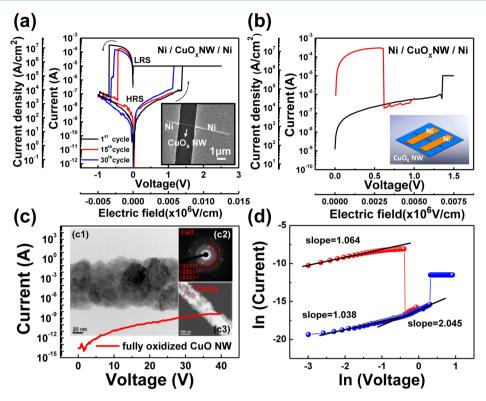

During the resistive switching measurements, a compliance current (CC) was set to protect the devices from the hard breakdown, which would result in the permanent failure. Figure 5a represents typical I-V characteristics in a Ni/CuO<sub>x</sub> NW/Ni device. The SEM image of corresponding device configuration is shown in the inset. When a DC voltage sweep was applied from 0 to 2.5 V with a compliance current of 10  $\mu$ A, a sudden increase of current was observed at  $\sim 1.375$  V. The resistance changes from pristine resistance state to low-resistance state (LRS or ON-state), defined as the "SET" process, and the corresponding applied voltage is called SET voltage  $(V_{\rm SET})$ . Subsequently, when the voltage bias was swept from 0 to -1 V, the resistance of the device transited back to high-resistance state (HRS or OFF-state), which is called the "RESET process" and the corresponding voltage, is called RESET voltage  $(V_{RESET})$ . This kind of resistive switching whose SET/RESET voltages having an opposite polarity is called bipolar switching.

Figure 3. TEM analyses of Cu and  $CuO_x$  NW. (a) Bright field image of a typical Cu NW. (b) High resolution TEM image of Cu NW. Inset shows the corresponding selected area diffraction pattern obtained by FFT process. (c) Bright field image of a  $CuO_x$  NW. (d) High resolution TEM image of a  $CuO_x$  NW. Insets show the corresponding selected area diffraction patterns obtained by FFT process. (e) HAADF image of a  $CuO_x$  NW. Inset shows the EELS mapping images at Cu L-edge and O K-edge from the selected region.

**Figure 4.** Electrical I-V characteristics of Cu NW and CuO<sub>x</sub> NW. (a) Distinctive metallic behavior can be found. Inset shows a typical Ohmic behavior in logarithm scale. (b) Dramatic current drop occurs to Cu NW NW once the bias was applied over 0.6 V whereas no current change to CuO<sub>x</sub> occurs at applied bias <1.2 V.

In addition, Figure Sb shows unipolar switching of the  $\text{CuO}_x$  NW devices. The results indicate that the  $\text{CuO}_x$  NW devices actually exhibit a nonpolar switching behavior in the symmetric MIM configuration. However, the unipolar switching is not stable (Figure S2, Supporting Information) and reversible switching can be observed only when the devices are operated in bipolar mode. More typical bipolar switching I-V curves are shown in Figure S3 (Supporting Information). It is clearly seen that the threshold voltages of SET and RESET are relatively small ( $\sim$ 1 V) in either switching mode. Besides, the requirement of forming process to activate resistive switching operation is one of the critical issues for ReRAM practical

application. It is quite interesting that the CuO<sub>x</sub> NW could trigger a resistive switch effect without a "forming process". Note that the  $V_{\text{SET}} = 1.375 \text{ V}$  with an electric field of about ~6.8 kV/cm is relatively small, having the potential to reduce the power consumption. For comparison, Table 1 tabulates the performance of devices in this work and the presents copper oxide-based resistive switching memories reported in the previous literature. In general, threshold voltage is proportional to film thickness/distance between the two electrodes. The threshold electric field in CuO<sub>x</sub> nanowire device is much smaller than those of thin films cases. Furthermore, the operation with the small bias and forming-free property of the polycrystalline CuO<sub>x</sub> nanowire is attractive when compared with the other single crystalline nanowire-based memristor works. 19–21,24,32 In addition, the fully oxidized nanowires were synthesized by extending the annealing time (20 h of annealing), where the originally smooth surface of the nanowire was converted to the rough one shown in Figure 5c1. It is because of the different volume change during formation of many small aggregated CuO<sub>x</sub> grains. The corresponding SAED of the fully oxidized CuO<sub>x</sub> nanowire is shown in Figure 5c2, for which the (111) plane of CuO was indexed. Cavity regions were clearly observed in the HAADF image (Figure 5c3), which is most likely owing to the volume change of the phase transformation from Cu to CuO<sub>x</sub>. The current-voltage (I-V) characteristics of fully oxidized CuO, nanowires are shown in Figure 5c. It is noted that the device did not exhibit a resistive switching behavior even when the bias was applied up to 40 V. That is, the resistive switching properties only occur in the partially oxidized CuO<sub>x</sub> nanowires. Figure 5d shows the double-logarithmic I-V plot of the Ni/CuO<sub>x</sub> NW/Ni devices. Obviously, a linear proportion at HRS from the log I-V plot indicates an Ohmic conduction behavior  $(I \propto V)$  at a low voltage region (<1 V) and gradually changes to the Child's law region,<sup>34</sup> for which the current is proportional to the square of the voltage  $(I V^2)$ . This behavior is qualitatively interpreted to follow the shallow trap-associated space charge limited current (SCLC) theory with an equation of  $I(V) = aV + bV^{2.34}$

Figure 5. (a) Typical bipolar resistive switching I-V characteristic of Ni/CuO<sub>x</sub> NW/Ni device in logarithm scale. Inset shows a SEM image of a Ni/CuO<sub>x</sub> NW/Ni device. The distance between two electrodes of  $\sim 2~\mu m$  can be found. (b) Typical unipolar resistive switching I-V characteristics of Ni/CuO<sub>x</sub> NW/Ni devices in logarithm scale. Inset shows a schematic of a Ni/CuO<sub>x</sub> NW/Ni device. (c) Electrical I-V characteristics of fully oxidized CuO NW. (c1) Bright field TEM image shows the rough surface. (c2) Corresponding SAED pattern. (c3) Dark field TEM image reveals the existence of the cavity. (d) Corresponding double-logarithmic I-V curves.

Table 1. Summary of Copper Oxide based Resistive Switching Memories

| device<br>structure                             | thickness (electrode distance) | $V_{ m set} \  m (V)$ | $\frac{E_{ m set}}{({ m MV/cm})}$ | ref          |

|-------------------------------------------------|--------------------------------|-----------------------|-----------------------------------|--------------|

| Cu/Cu <sub>2</sub> O/<br>Ni                     | 6-8 nm                         | 1.6                   | 2.29                              | 9            |

| $Cu/Cu_2O/Ti$                                   | 12 nm                          | 2.7                   | 2.25                              | 40           |

| Cu/Cu <sub>2</sub> O/<br>Ni                     | 12 nm                          | 3.3                   | 2.75                              | 41           |

| $\begin{array}{c} TiN/CuO_x \\ /Pt \end{array}$ | 70 nm                          | 0.83                  | 0.12                              | 42           |

| Cu/CuO/Al                                       | 250 nm                         | 2.7                   | 0.108                             | 43           |

| Pt/CuO/Au                                       | 300 nm                         | 3.7                   | 0.123                             | 44           |

| Pt/Cu <sub>2</sub> O/Pt                         | 190 nm                         | 2.6                   | 0.137                             | 45           |

| Pt/CuO/Pt                                       | $2.1~\mu\mathrm{m}$            | 12                    | $5.71 \times 10^{-2}$             | 46           |

| Ni/CuO <sub>x</sub>                             | $2~\mu\mathrm{m}$              | 1.35                  | $6.75 \times 10^{-3}$             | this<br>work |

| NW/Ni                                           |                                |                       |                                   |              |

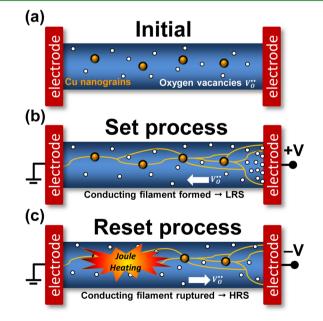

In general, pristine-state oxide materials are too insulative to induce reliable resistive switching due to the low density of defects such as oxygen vacancies or metal interstitials. Therefore, an electroforming process is a prerequisite to operate a device, which is an obstacle for ReRAM commercial applications. In the case of the present work, there is a significant amount of oxygen vacancies ( $V_{\rm O}$ ) in CuO<sub>x</sub> NW due to the coexistence of Cu<sub>2</sub>O/CuO and Cu nanograins, which triggers a low electric-field-induced switching operation with the forming free behavior, as shown in Figure 6a. During the SET process, as shown in Figure 6b, oxygen vacancies diffuse from the anode (the electrode on which the voltage was

**Figure 6.** Schematics of resistive switching mechanism. (a) Initial state before set process, (b) set process, and (c) reset process.

applied) to cathode (grounded electrode) and form metallic filaments under the electric field. Extra oxygen vacancies can be generated at the interface between  $\text{CuO}_x$  NW and anode. Simultaneously, electrons are injected from cathode to anode. The Joule heating effect by electron injection should provide a thermal energy to drive ionic migration. The metallic Cu

components, as nanoparticles embedded in the CuO<sub>x</sub> nanowire, enhance the diffusion of mobile oxygen vacancies and induce local electric field enhancement.<sup>37,38</sup> In addition, the geometry of a confined nanowire configuration offers a large area surface and a direct moving path for diffusion of oxygen vacancies to induce the stable switching. In the RESET process, a significant amount of heat generated by the Joule heating interrupts the local filaments and the conducting paths of electron are broken when high current density flows into the metallic filaments (Figure 6c). Simultaneously, Joule heating also provides energy to the thermochemical reaction, causing the migration of oxygen vacancies (oxygen ions). Notice that positions for the rupture of the filaments would normally occur near the grounded electrode because of much finer filament sizes.<sup>39</sup> As a result, both Joule heating and electric field play an important role in resistive switching, simultaneously. 4,35 However, the interruption of the conducting filaments is mainly due to the Joule heating in the nonpolar device. 4,35,36 Yet, the migration of oxygen vacancies under the positive bias results in the formation or the reconstruction of the conducting filaments. Different stabilities of resistive switching between unipolar and bipolar mode are observed. When the devices are manipulated in the unipolar mode, oxygen vacancies would consecutively drift to the cathode under the positive bias. As a result, it is likely that conducting filaments would be formed again right after the Joule heating takes place (Figure S2b, Supporting Information). On the other hand, the diffusion of oxygen vacancies by an electric field would localize the formation and rupture of conducting filaments near the grounded electrode when the devices are manipulated in bipolar mode. 35,36 Therefore, the migration of oxygen vacancies also enhances the switching stability.

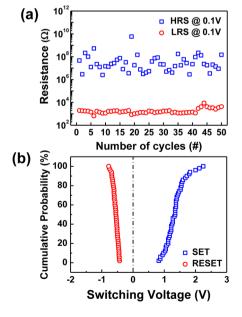

Figure 7a shows the switching endurance tests of nanowire devices. Obtained by repetitive ON/OFF sweeping operation, the endurance cycling test could reach to 50 times. The memory window is defined by the two resistance states as  $(R_{\rm OFF}-R_{\rm ON})/R_{\rm ON}\approx R_{\rm OFF}/R_{\rm ON}$ . The typical resistances of the

Figure 7. (a) Endurance test of the Ni/CuO<sub>x</sub> NW/Ni device under DC voltage sweep mode at read voltage of 0.1 V. (b) Cumulative distribution plot of  $V_{\rm SET}$  and  $V_{\rm RESET}$  for the Ni/CuO<sub>x</sub> NW/Ni device.

ON-state are an order of  $10^3 \Omega$  and those of the OFF-state are on the order of  $10^6 \sim 10^9 \Omega$ , showing that the memory window is more than 10<sup>3</sup>. Statistical results of HRS and LRS in the different nanowire devices are shown in Figure S4 (Supporting Information). The larger the memory window, the less chance for misreading of the resistance states, and it also has the potential for high density multistate memory application by using different compliance currents.<sup>39</sup> The dynamic responses of CuO<sub>x</sub> NW devices were also performed, as shown in Figure S5 (Supporting Information), showing the potential for real applications during the consecutive pulse measurements. Clearly, ON/OFF ratios are still 3 orders of magnitude compared with DC sweep endurance data. Furthermore, we have applied a smaller pulse (50  $\mu$ s) to devices but none of them show the resistive switching due to the micrometer scale  $(\sim 2 \mu m)$  channel length of our devices. We postulate that a quicker response of devices can be expected at a smaller channel length. Figure 7b shows cumulative probability distributions of SET and RESET voltages ( $V_{\text{SET}}$  and  $V_{\text{RESET}}$ ) for different switching cycles performed on the Ni/CuO<sub>x</sub> NW/ Ni device. The  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  distribute in the ranges of 0.875 to 2.25 V and -0.43 to -0.78 V, respectively. The variation of  $V_{

m RESET}$  is much more narrower than that of  $V_{

m SET}$ , which is evidence that conducting filaments play a dominant role in resistive switching characteristics in a single CuO<sub>x</sub> NW. Judging from the filamentary resistive switching mechanism, the formation of conducting filament in the SET process should be more random than the rupture of an existing filament during the RESET process.<sup>35</sup> Therefore, the formation process is determined by the competition among different filamentary paths with variable locations, random orientations, and uncertain sizes of conducting filaments.8 Because the RESET process is caused by the Joule heating effect to burn out the existing filament paths, a larger distribution in  $V_{

m SET}$  should be expected. The switching cycle performance is still limited by the breakdown of the nanowire owing to the Joule heating effect, which is expected to be improved in our following work. However, the resistive switching property could be operated in a single CuO<sub>x</sub> NW ~50 nm in diameter. In other words, it confirms that the ReRAM device could be scaled down to the 50 nm region.

# 4. CONCLUSIONS

In summary, the resistive switching effect in  $\text{CuO}_x$  NW synthesized by a low-cost and large-scale electrochemical process with AAO nanotemplates at low temperatures was successfully demonstrated. The  $\text{CuO}_x$  NW memory devices exhibit a forming-free property, low electric-field-induced switching operation because of a significant amount of defects and Cu nanocrystals in the  $\text{CuO}_x$  nanowires. Detailed resistive switching mechanisms are systematically proposed and investigated. This work is expected to have not only have the opportunity to help in the exploration of forming-free resistive switching mechanisms but also the potential to improve performance for resistive memory devices.

## ASSOCIATED CONTENT

## **S** Supporting Information

EELS Cu  $L_{2,3}$  edge spectra of the  $CuO_x$  NW; unipolar operation of  $CuO_x$  NW; device yield; statistical results of HRS and LRS, switching endurance data of the  $CuO_x$  NW device. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*Y.-L. Chueh. E-mail: ylchueh@mx.nthu.edu.tw.

#### **Author Contributions**

§These two authors contributed equally to this work.

#### **Notes**

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The research was supported by the Ministry of Science and Technology through Grant Nos. 101-2112-M-007-015-MY3, 101-2218-E-007-009-MY3, 102-2633-M-007-002, and National Tsing Hua University through Grant No. 102N2022E1. Y. L. Chueh greatly appreciates the use of facility at CNMM the National Tsing Hua University through Grant No. 102N2744E1.

## REFERENCES

- (1) Waser, R.; Aono, M. Nanoionics-based Resistive Switching Memories. *Nat. Mater.* **2007**, *6*, 833–840.

- (2) Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Redox-based Resistive Switching Memories Nanoionic Mechanisms, Prospects, and Challenges. *Adv. Mater.* **2009**, *21*, 2632—2663.

- (3) Sawa, A. Resistive Switching in Transition Metal Oxides. *Mater. Today* **2008**, *11*, 28–36.

- (4) Yang, J. J.; Strukov, D. B.; Stewart, D. R. Memristive Devices for Computing. *Nat. Nanotechnol.* **2013**, *8*, 13–24.

- (5) Baek, I. G.; Lee, M. S.; Seo, S.; Lee, M. J.; Seo, D. H.; Suh, D. S.; Park, J. C.; Park, S. O.; Kim, H. S.; Yoo, I. K.; Chung, U. I.; Moon, J. T. Highly Scalable Nonvolatile Resistive Memory Using Simple Binary Oxide Driven by Asymmetric Unipolar Voltage Pulses. In *Electron Devices Meeting*, 2004: IEDM Technical Digest, San Francisco, CA, December 13–15, 2004; IEEE International: New York, 2004; pp 587–590.

- (6) Choi, B. J.; Jeong, D. S.; Kim, S. K.; Rohde, C.; Choi, S.; Oh, J. H.; Kim, H. J.; Hwang, C. S.; Szot, K.; Waser, R.; Reichenberg, B.; Tiedke, S. Resistive Switching Mechanism of TiO<sub>2</sub> Thin Films Grown by Atomic-Layer Deposition. *J. Appl. Phys.* **2005**, *98*, 033715–10.

- (7) Chang, W.-Y.; Lai, Y.-C.; Wu, T.-B.; Wang, S.-F.; Chen, F.; Tsai, M.-J. Unipolar Resistive Switching Characteristics of ZnO Thin Films for Nonvolatile Memory Applications. *Appl. Phys. Lett.* **2008**, 92, 022110–022110-3.

- (8) Huang, C.-H.; Huang, J.-S.; Lin, S.-M.; Chang, W.-Y.; He, J.-H.; Chueh, Y.-L.  $ZnO_{1-x}$  Nanorod Arrays/ZnO Thin Film Bilayer Structure: From Homojunction Diode and High-Performance Memristor to Complementary 1D1R Application. *ACS Nano* **2012**, *6*, 8407–8414.

- (9) Tzu-Ning, F.; Kaza, S.; Haddad, S.; An, C.; Yi-Ching, W.; Zhida, L.; Avanzino, S.; Dongxiang, L.; Gopalan, C.; Seungmoo, C.; Mahdavi, S.; Buynoski, M.; Lin, Y.; Marrian, C.; Bill, C.; VanBuskirk, M.; Taguchi, M. Erase Mechanism for Copper Oxide Resistive Switching Memory Cells with Nickel Electrode. In *Electron Devices Meeting*, 2006: *IEDM '06*, San Francisco, CA, December 11–13, 2006; IEEE International: New York, 2006.

- (10) Qi, J.; Olmedo, M.; Ren, J.; Zhan, N.; Zhao, J.; Zheng, J.-G.; Liu, J. Resistive Switching in Single Epitaxial ZnO Nanoislands. *ACS Nano* **2012**, *6*, 1051–1058.

- (11) Nagashima, K.; Yanagida, T.; Oka, K.; Kanai, M.; Klamchuen, A.; Kim, J.-S.; Park, B. H.; Kawai, T. Intrinsic Mechanisms of Memristive Switching. *Nano Lett.* **2011**, *11*, 2114–2118.

- (12) Nagashima, K.; Yanagida, T.; Oka, K.; Kanai, M.; Klamchuen, A.; Rahong, S.; Meng, G.; Horprathum, M.; Xu, B.; Zhuge, F.; He, Y.; Park, B. H.; Kawai, T. Prominent Thermodynamical Interaction with Surroundings on Nanoscale Memristive Switching of Metal Oxides. *Nano Lett.* **2012**, *12*, 5684–5690.

- (13) Oka, K.; Yanagida, T.; Nagashima, K.; Kanai, M.; Kawai, T.; Kim, J.-S.; Park, B. H. Spatial Nonuniformity in Resistive-Switching Memory Effects of NiO. *J. Am. Chem. Soc.* **2011**, *133*, 12482–12485.

- (14) Ielmini, D.; Cagli, C.; Nardi, F.; Zhang, Y. Nanowire-based Resistive Switching Memories: Devices, Operation and Scaling. *J. Phys. D: Appl. Phys.* **2013**, *46*, 074006.

- (15) Hu, J.; Odom, T. W.; Lieber, C. M. Chemistry and Physics in One Dimension: Synthesis and Properties of Nanowires and Nanotubes. *Acc. Chem. Res.* **1999**, *32*, 435–445.

- (16) Xia, Y.; Yang, P.; Sun, Y.; Wu, Y.; Mayers, B.; Gates, B.; Yin, Y.; Kim, F.; Yan, H. One-Dimensional Nanostructures: Synthesis, Characterization, and Applications. *Adv. Mater.* **2003**, *15*, 353–389.

- (17) Barth, J. V.; Costantini, G.; Kern, K. Engineering Atomic and Molecular Nanostructures at Surfaces. *Nature* **2005**, 437, 671–9.

- (18) Kim, S. I.; Lee, J. H.; Chang, Y. W.; Hwang, S. S.; Yoo, K.-H. Reversible Resistive Switching Behaviors in NiO Nanowires. *Appl. Phys. Lett.* **2008**, *93*, 033503.

- (19) Oka, K.; Yanagida, T.; Nagashima, K.; Tanaka, H.; Kawai, T. Nonvolatile Bipolar Resistive Memory Switching in Single Crystalline NiO Heterostructured Nanowires. *J. Am. Chem. Soc.* **2009**, *131*, 3434–3435.

- (20) Oka, K.; Yanagida, T.; Nagashima, K.; Kawai, T.; Kim, J.-S.; Park, B. H. Resistive-Switching Memory Effects of NiO Nanowire/Metal Junctions. *J. Am. Chem. Soc.* **2010**, *132*, 6634–6635.

- (21) Nagashima, K.; Yanagida, T.; Oka, K.; Taniguchi, M.; Kawai, T.; Kim, J.-S.; Park, B. H. Resistive Switching Multistate Nonvolatile Memory Effects in a Single Cobalt Oxide Nanowire. *Nano Lett.* **2010**, 10, 1359–1363.

- (22) Chiang, Y. D.; Chang, W. Y.; Ho, C. Y.; Chen, C. Y.; Ho, C. H.; Lin, S. J.; Wu, T. B.; He, J. H. Single-ZnO-Nanowire Memory. *IEEE Trans. Electron Devices* **2011**, *58*, 1735–1740.

- (23) Yang, Y. C.; Zhang, X. X.; Gao, M.; Zeng, F.; Zhou, W. Y.; Xie, S. S.; Pan, F. Nonvolatile Resistive Switching in Single Crystalline ZnO Nanowires. *Nanoscale* **2011**, *3*, 1917–1921.

- (24) Deng, X. L.; Hong, S.; Hwang, I.; Kim, J. S.; Jeon, J. H.; Park, Y. C.; Lee, J.; Kang, S. O.; Kawai, T.; Park, B. H. Confining Grains of Textured Cu<sub>2</sub>O Films to Single-Crystal Nanowires and Resultant Change in Resistive Switching Characteristics. *Nanoscale* **2012**, *4*, 2029–33.

- (25) Dong, H.; Zhang, X.; Zhao, D.; Niu, Z.; Zeng, Q.; Li, J.; Cai, L.; Wang, Y.; Zhou, W.; Gao, M.; Xie, S. High Performance Bipolar Resistive Switching Memory Devices Based on Zn<sub>2</sub>SnO<sub>4</sub> Nanowires. *Nanoscale* **2012**, *4*, 2571–2574.

- (26) Hsu, C. W.; Chou, L. J. Bipolar Resistive Switching of Single Gold-in-Ga<sub>2</sub>O<sub>3</sub> Nanowire. *Nano Lett.* **2012**, *12*, 4247–53.

- (27) Teichert, C. Self-Organization of Nanostructures in Semi-conductor Heteroepitaxy. *Phys. Rep.* **2002**, *365*, 335–432.

- (28) Lai, C.-C.; Lin, Y.-K.; Yuan, F.-W.; Tuan, H.-Y.; Chueh, Y.-L. High-Density Germanium Nanowire Arrays via Supercritical Fluid-Liquid-Solid Growth in Porous Alumina Templates. *ECS Solid-State Lett.* **2013**, *2*, P55–P57.

- (29) Lee, W.; Ji, R.; Gosele, U.; Nielsch, K. Fast Fabrication of Long-Range Ordered Porous Alumina Membranes by Hard Anodization. *Nat. Mater.* **2006**, *5*, 741–7.

- (30) Masuda, H.; Fukuda, K. Ordered Metal Nanohole Arrays Made by a Two-Step Replication of Honeycomb Structures of Anodic Alumina. *Science* **1995**, 268, 1466–1468.

- (31) Huang, Q.; Lilley, C. M.; Bode, M.; Divan, R. Surface and Size Effects on the Electrical Properties of Cu Nanowires. *J. Appl. Phys.* **2008**, *104*, 023709–023709-6.

- (32) Cagli, C.; Nardi, F.; Harteneck, B.; Tan, Z.; Zhang, Y.; Ielmini, D. Resistive-Switching Crossbar Memory Based on Ni-NiO Core-Shell Nanowires. *Small* **2011**, *7*, 2899–905.

- (33) Mu, C.; He, J. Confined Conversion of CuS Nanowires to CuO Nanotubes by Annealing-Induced Diffusion in Nanochannels. *Nanoscale Res. Lett.* **2011**, *6*, 150.

- (34) Lampert, M. A. Simplified Theory of Space-Charge-Limited Currents in an Insulator with Traps. *Phys. Rev.* **1956**, *103*, 1648–1656.

- (35) Yang, J. J.; Inoue, I. H.; Mikolajick, T.; Hwang, C. S. Metal Oxide Memories Based on Thermochemical and Valence Change Mechanisms. *MRS Bull.* **2012**, *37*, 131–137.

- (36) Kyung Min, K.; Doo Seok, J.; Cheol Seong, H. Nanofilamentary Resistive Switching in Binary Oxide System: A Review on the Rresent Status and Outlook. *Nanotechnology* **2011**, *22*, 254002.

- (37) Chang, W.-Y.; Cheng, K.-J.; Tsai, J.-M.; Chen, H.-J.; Chen, F.; Tsai, M.-J.; Wu, T.-B. Improvement of Resistive Switching Characteristics in  $TiO_2$  Thin Films with Embedded Pt Nanocrystals. *Appl. Phys. Lett.* **2009**, *95*, 042104.

- (38) Yoon, D. H.; Kim, S. J.; Jung, J.; Lim, H. S.; Kim, H. J. Low-voltage Driving Solution-Processed Nickel Oxide Based Unipolar Resistive Switching Memory with Ni Nanoparticles. *J. Mater. Chem.* **2012**, 22, 17568–17572.

- (39) Huang, C.-H.; Huang, J.-S.; Lai, C.-C.; Huang, H.-W.; Lin, S.-J.; Chueh, Y.-L. Manipulated Transformation of Filamentary and Homogeneous Resistive Switching on ZnO Thin Film Memristor with Controllable Multistate. ACS Appl. Mater. Interfaces 2013, 5, 6017–6023.

- (40) Chen, A.; Haddad, S.; Wu, Y. C.; Lan, Z.; Fang, T. N.; Kaza, S. Switching Characteristics of Cu<sub>2</sub>O Metal-Insulator-Metal Resistive Memory. *Appl. Phys. Lett.* **2007**, *91*, 123517.

- (41) Chen, A.; Haddad, S.; Wu, Y. C.; Fang, T. N.; Kaza, S.; Lan, Z. Erasing Characteristics of Cu<sub>2</sub>O Metal-Insulator-Metal Resistive Switching Memory. *Appl. Phys. Lett.* **2008**, *92*, 013503.

- (42) Yang, W.-Y.; Kim, W.-G.; Rhee, S.-W. Radio Frequency Sputter Deposition of Single Phase Cuprous Oxide Using  $Cu_2O$  as a Target Material and its Resistive Switching Properties. *Thin Solid Films* **2008**, 517, 967–971.

- (43) Lv, H.; Wang, M.; Wan, H.; Song, Y.; Luo, W.; Zhou, P.; Tang, T.; Lin, Y.; Huang, R.; Song, S.; Wu, J. G.; Wu, H. M.; Chi, M. H. Endurance Enhancement of Cu-Oxide based Resistive Switching Memory with Al Top Electrode. *Appl. Phys. Lett.* **2009**, *94*, 213502.

- (44) Kim, C. H.; Jang, Y. H.; Hwang, H. J.; Sun, Z. H.; Moon, H. B.; Cho, J. H. Observation of Bistable Resistance Memory Switching in CuO Thin Films. *Appl. Phys. Lett.* **2009**, *94*, 102107.

- (45) Kang, S.-O.; Hong, S.; Choi, J.; Kim, J.-S.; Hwang, I.; Byun, I.-S.; Yun, K.-S.; Park, B. H. Electrochemical Growth and Resistive Switching of Flat-Surfaced and (111)-Oriented Cu<sub>2</sub>O Films. *Appl. Phys. Lett.* **2009**, 95, 092108.

- (46) Fujiwara, K.; Nemoto, T.; Rozenberg, M. J.; Nakamura, Y.; Takagi, H. Resistance Switching and Formation of a Conductive Bridge in Metal/Binary Oxide/Metal Structure for Memory Devices. *Jpn. J. Appl. Phys.* **2008**, *47*, 6266–6271.